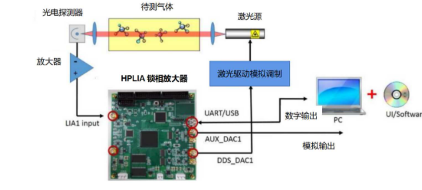

TDLAS用微型双通道调制解调锁相放大器是以当今FPGA +ARM单片机的业界主流配置而设计。浮点数数字信号处理的计算任务由 FPGA硬件加速完成,而结果数据采集和上位机交互由ARM单片机处理。为了提高性价比,系统以独立双输入输出通道为原则设计,从而在单板上实现双路锁相通道的应用。

锁相放大器(Lock-in Amplifier)是一种能够在极端噪音环境下提取一个已知载波频率信号的电子仪器。利用相位敏感检测技术(Phase Sensitive Detector, PSD),只有存在于特定参考频率的信号可以被挑选出来,而其他频率的噪声则不会被检出。锁相放大器能够检测极微弱的 AC 信号,即使在噪声高于信号数千倍的情况下也可实现精确的测量。传统的锁相放大器利用了模拟变频混频器和 RC 滤波器,它需要大量的模拟电路设计和优化模拟信号解调。如今,锁相放大器自身正在变革,先进的集成电路技术和快速数字信号处理(DSP)的应用替代了传统的模拟器件,可使其灵敏度提高数百倍。

• 参考频率内部同步,无需外部参考信号输入;

• 可解调低至10nV,中心频率500kHz微弱信号;

• 两路独立输入端,实现双通道锁相放大解调方案;

• 两路调制输出端,输出信号频率、幅度、偏置独立可调;

• 两路低速辅助模拟通道,实时输出解调运算结果;

• USB虚拟串口连接上位机,极简锁相控制界面;

• 尺寸小巧,易于便携及系统集成;

• 可根据用户需求,灵活定制FPGA算法。

综述 | |

尺寸大小 | 15.4x15.4x7.6cm3 |

重量 | 670 g |

电源供应 | DC 5V/2A (含电源板) |

模拟输入 | |

频率范围 | AC–0.5MHz |

输入阻抗 | 50 ohm |

输入噪声 | 10nV/Hz1/2 (>10 kHz) |

电压范围 | -1V to +1V |

输入增益 | 1, 10 |

模/数转换 | 14 bit; 4 MSa/s |

模拟输出 | |

输出 | 2 channels; -1V to +1V |

频率范围 | DC–0.5MHz |

数/模转换 | 16 bit; 4 MSa/s |

锁相解调器 | |

解调器数量 | 2 channels |

时间常量 | 10ms, 1ms(可依用户需求制定) |

过滤带宽(Hz) | 1000, 100(可依用户需求制定) |

谐波 | 1F, 2F, 3F, 4F |

参考相位分辨率 | 1.0 degree |

暂无

如有意向购买产品或者相关技术咨询,请联系我们